# The Modular Multilevel Converter for High Step-Up Ratio DC–DC Conversion

Xiaotian Zhang, Member, IEEE, and Timothy C. Green, Senior Member, IEEE

Abstract—High step-up ratio dc-dc converters with megawatt ratings are of interest in wind turbine interfaces and high-voltage direct-current systems. This paper presents a modular multilevel dc-dc converter based on the standard boost converter topology but with the normal single switches replaced by a number of capacitor-clamped submodules. The converter is operated in resonant mode with resonance between submodule capacitors and the arm inductor. A phase-shifted switching arrangement is applied such that there is a constant number, i.e., N, of submodules supporting the high voltage at a time. In this operation mode, the step-up ratio is dependent on the number of submodules and the inductor charging ratio. The converter exhibits scalability without using a transformer and is capable of bidirectional power flow. An application example of a wind turbine interface with a 10: 1 conversion ratio is demonstrated in simulation. The experimental verification of the concept using a lab-scale prototype is provided.

Index Terms—DC transformer, high-voltage direct current (HVDC) converters, modular multilevel converters (MMCs), resonant conversion, step-up dc-dc conversion.

#### I. INTRODUCTION

ULTILEVEL converters used for medium-voltage and high-voltage applications significantly reduce the harmonic content of the output voltage as compared with the traditional two-level converters [1]-[4]. Multilevel converter schemes for dc-dc conversion are becoming popular [5] in renewable energy applications following the success of this approach in dc-ac conversion. There are many different types of multilevel converters developed [6], which can be directly or indirectly used as step-up dc-dc converters. The modular multilevel converter (MMC) is found to have more attractive features than the others. Diode-clamped converters have a large number of diodes required, and with the unbalancing issue, making the system impractical to implement. Conventional flying capacitor converters [7] require many capacitors connected in series. The total series capacitance is much smaller than that of a single one. Therefore, the total volume of capacitors required is quite high. Generalized multilevel converters can be used for step-up dc-dc conversion [8], [9], but the

Manuscript received May 27, 2014; revised September 22, 2014 and November 19, 2014; accepted December 27, 2014. Date of publication January 19, 2015; date of current version June 26, 2015. This work was supported by the Engineering and Physical Sciences Research Council, U.K., under Grant EP/K006312/1.

The authors are with the Department of Electrical Engineering, Imperial College London, London, SW7 2AZ, U.K. (e-mail: xiaotian. zhang@imperial.ac.uk; t.green@imperial.ac.uk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2015.2393846

topology results in a large size when the step ratio is high. Other topologies such as input-parallel output-series (IPOS) converters [10] and switched capacitor converters have been proposed and developed for step-up dc-dc conversion [11]-[13]. The IPOS converters use resonant submodules to achieve high-power conversion and efficiency [14], but the main disadvantage is the requirement of a large number of isolation transformers, which have high potential differences between the windings. Switched capacitor converters with series-parallel topologies are subject to incremental voltage stress either on the module switch or on the module capacitor. The highest voltage stress is close to the output (high-side) dc voltage. The switched capacitor converters are also subject to high charge losses and overshoot currents. This problem can be mitigated by driving metal-oxide-semiconductor field-effect transistors (MOSFETs) with very high switching frequency. Therefore, switched capacitor converters are only used under a low-voltage condition. A power-electronics-based Cockcroft-Walton multiplier has been demonstrated in [15]. This is a light and cheap solution for high-voltage dc experiments when only unidirectional step-up conversion is required. A bidirectional mediumvoltage "ladder"-shaped dc-dc converter is proposed in [16], which can achieve a high step ratio. The advantage is that the converter does not require synchronization of switching between submodules. However, the current ratings in different submodules are not the same, and the inductor currents close to the low-voltage side are high.

In medium- and high-voltage applications, MMCs used for dc–dc conversion are emerging technologies [5], [17]. These converters are based on conventional MMCs [18]–[20]. MMCs usually require a complicated balancing control scheme to maintain the voltage levels. However, they provide more than two levels and good waveform quality. Cells with fault can also be bypassed while keeping the system operational. High modularity and redundancy are the main advantages of MMCs.

Until now, there has been no direct and simple solution for large step-up ratio dc-dc conversion using the MMC approach. This paper presents a new topology and control scheme of a modular multilevel bidirectional dc-dc converter with high step-up ratio. It is based on the conventional boost converter with groups of submodules placed in both the diode and switch positions. The proposed converter can achieve a high step ratio. Phase-shifted pulsewidth modulation (PWM) is used to achieve a high effective operating frequency for a given submodule switching frequency. The proposed converter is bidirectional and suitable for low-power dc-dc applications as it has the feature of modularity, simplicity, and flexibility. The configuration of the circuit and its operation principle are presented and verified by experimental results from a downscaled prototype.

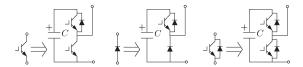

Fig. 1. Single switches and submodules with active clamping.

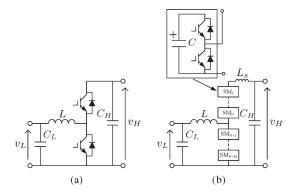

Fig. 2. Bidirectional dc–dc converters. (a) Conventional two-level dc–dc converter. (b) Novel modular multilevel dc–dc converter.

# II. BIDIRECTIONAL MODULAR MULTILEVEL DC-DC CONVERTERS

In converting a simple standard switched-mode circuit to a modular multilevel format, a variety of capacitor-clamped submodules are required. Fig. 1 shows clamped single switches that use the half-bridge configuration in which replacements for a single insulated-gate bipolar transistor (IGBT), a diode, and an IGBT with an antiparallel diode are illustrated. The ability to clamp the off-state voltage across a switch when a stack of switches is connected in series is crucial in forming MMC topologies. Using this idea, the modular multilevel inverter topology was generated by clamping the series-connected IGBTs in the conventional two-level inverter. With active clamping, each switch has a well-defined voltage and good sharing between submodules.

The active-clamping idea can also be applied to dc–dc converters. The upper IGBT in the half bridge is termed as clamping IGBT, whereas the lower IGBT is termed as clamped IGBT. The classic bidirectional two-level dc–dc converter is shown in Fig. 2(a). It consists of an inductor on the low-voltage side, two IGBTs with antiparallel diodes, and capacitors on both input and output sides. Replacing all the switches by seriesconnected submodules with active clamping, the bidirectional buck–boost converter becomes the modular multilevel dc–dc converter shown in Fig. 2(b). The number of upper submodules is not required to be the same as the number of the lower submodules; however, special operation techniques are required.

# III. HIGH STEP-UP RATIO MODULAR MULTILEVEL DC-DC CONVERTER

This section describes the operation method for the proposed dc–dc converter. The analysis focuses on step-up dc–dc conversion. To simplify the analysis, the theoretical developments are based on the following assumptions.

1) The switches are ideal, and the submodules are identical.

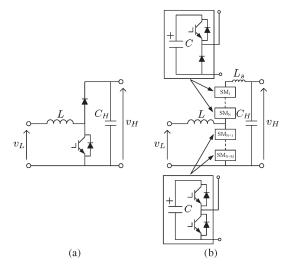

Fig. 3. Unidirectional step-up dc–dc converters. (a) Conventional boost converter. (b) Proposed modular multilevel step-up dc–dc converter.

- 2) The converter is lossless.

- 3) In steady state, the capacitor dc voltages are balanced.

# A. System Configuration

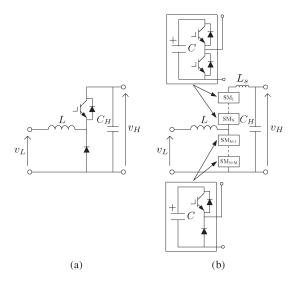

The configuration of the step-up conversion is provided to demonstrate the concept. The most commonly used boost converter topology with a single IGBT and a single diode is shown in Fig. 3(a). The IGBT in the lower position is used for charging the input inductor L. The diode in the upper position of the circuit is automatically commutated on when the inductor is discharging current to the high-voltage capacitor  $C_H$ . Applying active clamping (see Fig. 1) to the two switches, the modular multilevel unidirectional step-up converter with two stacks of submodules is obtained as shown in Fig. 3(b). The number of the half-bridge (clamped IGBT) submodules in the lower position is M. The number of the chopper (clamped diode) submodules in the upper position is N. The output (high-side) voltage is approximately equal to the sum of capacitor voltages of the stack of submodules once duty cycles are accounted for. There will be small differences between the instantaneous voltage across the stack (as submodules switch) and the voltage across  $C_H$ , and this is accommodated by including the small inductor  $L_S$ . A large capacitor  $C_L$  would normally be present at the input (low voltage) side. The step-down conversion is configured using the similar concept. The circuit of the proposed converter for step-down operation is shown in Fig. 4.

#### B. Phase-Shift Control

The proposed converter has various operating modes resulting in different operating features and step-up ratios. Apart from the high step-up ratio operation mode, which is the focus of this paper, the converter can also be used for high step-down ratio dc-dc conversion providing power for an auxiliary electronic circuit in medium-voltage systems. Moreover, with similar numbers of submodules in the upper stack and the lower stack, the converter can also be used for low-step-ratio high-voltage dc-dc conversion. Phase-shifted PWM is used to control the modular multilevel step-up dc-dc converter.

Fig. 4. Unidirectional step-down dc-dc converters. (a) Conventional buck converter. (b) Proposed modular multilevel dc-dc converter.

Phase-shifted PWM is arranged with a high duty cycle such that only one submodule capacitor at a time is out of the series connection, and thus, the step-up ratio of the circuit becomes dependent on the number of upper cells N. The effective frequency of this excitation is much higher than the frequency of switching of an individual cell.

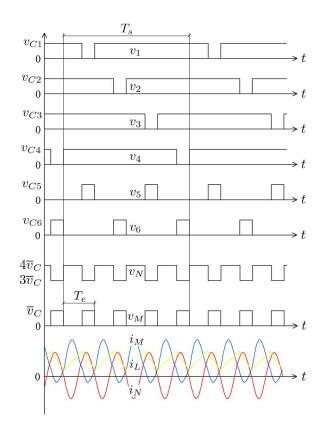

To demonstrate the principle of interleaved PWM, a step-up converter with four submodules in the diode position in the circuit of Fig. 3(b) is considered (N=4). To ensure that either four or three submodules are injecting voltage at any time, each must be operated with a duty cycle above 75%. For illustration, 90% is used. One module could be used in the lower position operating at four times the switching frequency of the upper modules (to give the same effective frequency). Instead, the system will be illustrated with two submodules in the lower position operating at twice the frequency of the upper submodules and with interleaved pulses. Assuming the submodule capacitor voltages to be constant, the key waveforms of the submodule voltages are shown in Fig. 5.

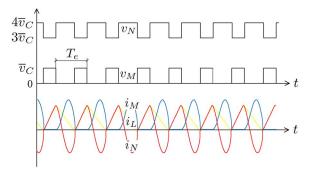

It can be seen in Fig. 5 that the upper (clamped diode) cells are synchronously switched with the lower (clamped IGBT) cells so that the total voltage of the upper cells  $v_N$  and lower cells  $v_M$  are complementary. This guarantees an almost constant dc voltage with a small ripple on the high-voltage side. The equivalent operating frequency is four times the switching frequency of the upper cells  $(f_e=4f_s)$  and is twice the switching frequency of the lower cells. As the frequency of the ripple on the high-voltage side is high, the passive components of the output filter do not need to be large. The current waveforms in Fig. 5 will be explained with the step-up operation.

The step-down operation has the same stack voltage waveforms as that of the step-up conversion. The voltage waveforms of the submodules are not shown. The time-domain waveforms of the stacks are shown in Fig. 6. In the step-down operation, the current directions and waveforms are different from that in the step-down operation. The operation of step-down conversion will be analyzed in detail in the following section.

Fig. 5. Time-domain key waveforms of the proposed step-up converter.

Fig. 6. Time-domain key waveforms of the proposed converter with step-down operation.

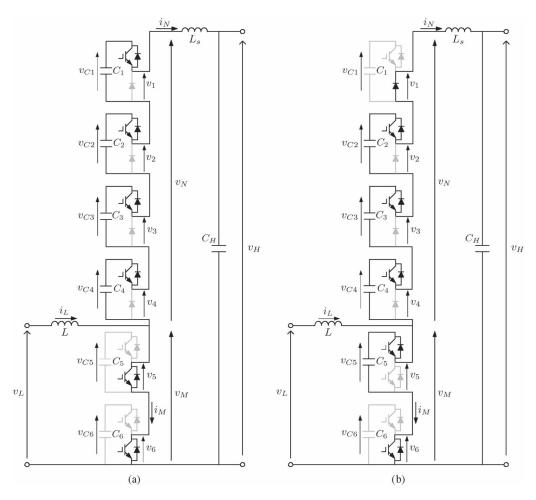

#### C. High Conversion Ratio

The proposed converter is aimed at high step-up ratio dc–dc conversion. The analysis of operation and conversion ratio will proceed by examining one equivalent cycle  $T_e$  in Fig. 5. Fig. 7 shows the detailed circuit diagrams with current paths highlighted for the two modes of the circuit. Mode 1 starts when the IGBT in Cell 4 is switched on and ends when the IGBT in Cell 1 switches off [see Fig. 7(a)]. The IGBT in Cell 1 switches off when the lower IGBT in Cell 5 switches off, and this defines the beginning of Mode 2 [see Fig. 7(b)]. Mode 2 ends when the IGBT of Cell 1 is switched on again. Modes 1 and 2 are analogous to the on- and off-states of the simple boost converter but with the difference that current can flow in both paths in both modes. The current flowing through the input inductor, upper cells (clamped diodes), and lower cells (clamped IGBTs) are defined as  $i_L$ ,  $i_N$ , and  $i_M$ , respectively.

Fig. 7. Step-up operation modes in the first equivalent operating cycle. (a) Mode 1. (b) Mode 2.

In Mode 1, the current  $i_L$  of inductor L is directly charged by the low-side (input) voltage  $v_L$  via the IGBTs in Cell 5 and Cell 6. The capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  are in series with the inductor  $L_s$  and the high-side (output) capacitor  $C_H$ , and together, they form a resonant tank. Because  $C_H$  is large and the cell capacitors are smaller and placed in series, the resonance is dominated by the cell capacitors, and  $C_H$  can be ignored. Therefore, the resonant frequency is

$$f_r = \frac{1}{2\pi\sqrt{L_sC/N}}. (1)$$

In the case of N=4,  $f_r=1/\pi\sqrt{L_sC}$ . When the converter enters Mode 2 from Mode 1, capacitor  $C_5$  is connected into the circuit, whereas capacitor  $C_1$  is out of series connection. The capacitors  $C_2$ ,  $C_3$ ,  $C_4$ , and  $C_5$  are in resonant tank with  $L_s$  and  $C_H$ . As the inductor L is relatively large, the current  $i_L$  is considered as from a current source. Therefore, the resonant frequency in Mode 2 is also dependent on four series-connected capacitors and the series inductor  $L_s$ . When the lower (clamped IGBT) cells and the upper (clamped diode) cells use the same capacitors, the resonant frequency in Mode 2 is the same as that in Mode 1.

In Fig. 7(b), it can be seen that the current  $i_N$  cannot be negative in Mode 2 because one cell (Cell 1 in the figure) is acting as a diode. If the actual resonant frequency is slightly

higher than  $f_e$ , by the end of Mode 2, the current  $i_N$  reaches zero, and the circuit operates in discontinuous conduction mode (DCM).

When Mode 1 begins, the current  $i_L$  is directly charged by the low-side voltage source. Meanwhile, the current  $i_N$  starts to resonate (starting from zero) with the frequency of  $f_r$ . The current  $i_M$  is  $i_L$  minus  $i_N$ . When the circuit enters Mode 2 from Mode 1, since  $v_{C5}$  is higher than  $v_L$ , the inductor current  $i_L$  reduces. As the circuit operates in DCM, before the end of the equivalent operating cycle, the current  $i_N$  falls to zero, and the current  $i_M$  is equal to  $i_L$  until a new cycle begins. The simulation result later in this paper will illustrate this.

To obtain the voltage conversion ratio, the charging ratio d is defined as the time duration of Mode 1 relative to the period, i.e.,  $T_e$  of the equivalent operating cycle. In steady state, the increase and decrease of  $i_L$  over a equivalent cycle  $T_e$  should be the same; hence,

$$\frac{v_L T_e d}{L} = \frac{(v_{Cj} - v_L) T_e (1 - d)}{L}$$

(2)

with j=5 or j=6. The capacitor voltages of the lower submodules can be written as

$$v_{Cj} = \frac{v_L}{1 - d}. (3)$$

The sum of average stack voltages  $v_N$  and  $v_M$  should be equal to the high-side voltage, i.e.,  $v_H$ , which yields

$$v_H = \frac{N - 1 + d}{N} \sum_{j=1}^{N} v_{Cj} + \frac{1 - d}{M} \sum_{j=N+1}^{N+M} v_{Cj}.$$

(4)

Under ideal conditions, the capacitor voltages are balanced and equal to  $\overline{v}_C$ . The voltage conversion ratio can be derived by substituting (3) into (4), i.e.,

$$\frac{v_H}{v_L} = \frac{N}{1 - d}. ag{5}$$

It can be seen that without increasing d, the conversion ratio can be increased by using higher numbers of upper submodules N. In the case of N=4, the conversion ratio is  $v_H/v_L=4/(1-d)$ .

The current stresses in the converter should be estimated because it is important in determining the power losses and device ratings. The low-side (input) inductor current  $i_L$  comprises a dc component and a sawtooth-shaped ripple. The average current of  $i_L$  can be derived from the power consumed on the high-voltage side. Here, it is assumed that the load dc current is  $I_o$ . Therefore,

$$I_L = \frac{v_H}{v_L} I_o. (6)$$

The peak-to-peak ripple  $\Delta I_L$  can be obtained from the charging time of inductor L, i.e.,

$$\Delta I_L = \frac{v_L T_e d}{L}.\tag{7}$$

The current stress on the clamped-diode (upper) stack depends on  $i_N$ . The dc component of  $i_N$  goes on to feed the load, and its ac component circulates within the resonant tank. It will be assumed that the ac component of  $i_N$  is approximately sinusoidal with a root mean square (RMS) value of  $I_{N1}$  at the resonant frequency. The power transferred out of the clamped-diode (upper) stack by the flow of the dc current is

$$P_1 = (N - 1 + d)\overline{v}_C I_o. \tag{8}$$

On the other hand, the ac voltage of the upper stack is a square wave with a peak-to-peak value of  $\overline{v}_C$ . Therefore, the RMS value of this square wave is  $\overline{v}_C/2$ . The power transferred into the stack by the sinusoidal resonant current interacting with the square-wave component of the stack voltage is

$$P_2 = \frac{\overline{v}_C}{2} I_{N1} \lambda \tag{9}$$

with  $\lambda$  as the power factor for this voltage and current combination. The value of  $\lambda$  can be obtained from numerical solutions. The maximum, i.e.,  $\lambda=1$ , is achieved when the charging ratio is d=0.5. If the converter is lossless, the dc power and ac power of the upper stack should be equal. Therefore

$$I_{N1} = \frac{N-1+d}{\lambda}I_o. ag{10}$$

After  $i_L$  and  $i_N$  are estimated, the current stress on the lower stack can be determined by  $i_M=i_L-i_N$ . A rough estimation of  $|i_M|<|i_L|+|i_N|$  can also be used.

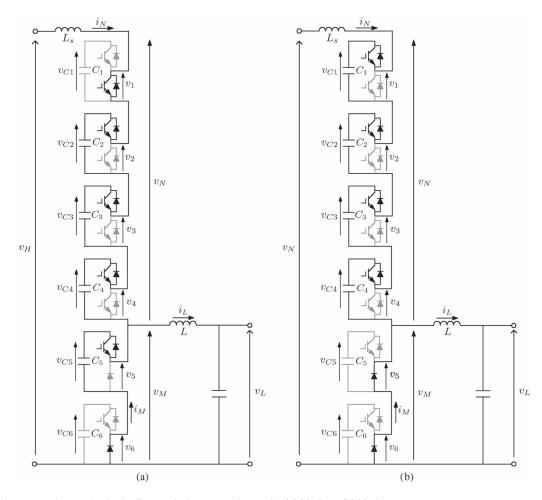

Although the converter is proposed for high step-up ratio dc–dc conversion, it also has the capability of step-down dc–dc conversion. Fig. 8 shows the detailed circuit diagrams with current paths highlighted for the two modes of the circuit. Mode 1 starts when the clamped IGBT in Cell 1 is switched on and ends when the clamped IGBT in Cell 1 is switched off [see Fig. 8(a)]. When the clamped IGBT in Cell 1 switches off and the clamping IGBT in Cell 5 switches off, the converter begins to enter Mode 2 [see Fig. 8(b)]. Mode 2 ends when the clamping IGBT of Cell 6 is switched off. For operation analysis, the current directions are defined opposite to the current directions in the step-up operation.

As the voltage on the inductor L in Mode 1 is higher than that in Mode 2, the current  $i_L$  of inductor L is charged in Mode 1 and discharged in Mode 2. During Mode 1, the inductor  $L_s$ and the capacitors  $C_2$ ,  $C_3$ , and  $C_4$  are charged, and therefore, the clamped diodes in the lower cells are reverse-biased. There is no current flowing through the lower stack. If the capacitor voltages are assumed to be constant, the currents  $i_L$  and  $i_N$ should linearly increase in Mode 1 and  $i_L$  equals  $i_N$ . The slight increase in the cell capacitor voltages does not affect the wave shapes obviously. When the converter enters Mode 2 from Mode 1, all the cell capacitors in the upper stack are in series with the inductor  $L_s$ . The inductor L starts to linearly discharge, and the clamped diode in Cell 6 is commutated. Meanwhile, the capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  in series with the inductor  $L_s$  form a resonant tank to discharge the energy stored in the passive components from Mode 1. The resonant frequency  $f_r$ in the step-down operation is the same as that in the step-up operation. Therefore, the current  $i_M$  flowing through the lower stack can be written as

$$i_M = i_L - i_N. (11)$$

This analysis for step-down operation explains the current waveforms in Fig. 6. The inductor current has a sawtooth wave shape, and the lower stack current is zero during Mode 1. In Mode 1, the upper stack current is equal to the inductor current. In Mode 2, the upper stack current is discharging with a resonant wave shape, which, together with the inductor current, determines the lower stack current. To derive the step-down output voltage  $v_L$  as a function of charging ratio d (defined in step-up operation) and high voltage  $v_H$ , the inductor current  $i_L$  is assumed to be the same after one equivalent charging cycle. Similar to the step-up operation, it can be approximated that  $Nv_{Cj} = v_H$ . The conversion ratio can be derived as

$$\frac{v_H}{v_L} = \frac{N}{1 - d}. (12)$$

The step-down operation has the same step ratio function as that in the step-up operation. This means that the proposed modular multilevel dc-dc converter is similar to the conventional bidirectional dc-dc converter in terms of step ratio. By changing the current directions, the converter achieves bidirectional power

Fig. 8. Step-down operation modes in the first equivalent operating cycle. (a) Mode 1. (b) Mode 2.

conversion and the same step ratio without modifying the switching arrangement.

#### D. Capacitor Voltage Clamping Mechanism

The converter has a cell capacitor voltage clamping mechanism. This property can be explained by using the stepup operation for example. As is shown in Fig. 7(a), when the low-voltage-side inductor is charging (Mode 1), there are capacitors of Cell 1, Cell 2, Cell 3, and Cell 4 supporting the high-side dc voltage. Since the resonant tank formed by the cell capacitors and inductor  $L_s$  has an impedance close to zero at the resonant frequency, the ac voltage drop across the resonant components is negligible. Therefore, the output high voltage is almost equal to  $v_o = v_{C1} + v_{C2} + v_{C3} + v_{C4}$ . In the next operation mode [see Fig. 7(b)], the output voltage can be expressed as  $v_o = v_{C2} + v_{C3} + v_{C4} + v_{C5}$ . Hence, by comparing the two equations, it can be stated that  $v_{C1} = v_{C5}$ . In the next operating cycle, using the same method, one can state that  $v_{C2} = v_{C6}$ . The following operation mode sequence in the remaining switching cycle gives  $v_{C1} = v_{C3} = v_{C5}$  and  $v_{C2} = v_{C4} = v_{C6}$ . The capacitor voltages of the upper cells are always clamped by the capacitor voltages of the lower cells. Therefore, by balancing the two lower cell capacitors, the dc voltages of all the capacitors should be equal in steady state. For the converter with only one cell in the lower position, the

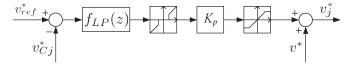

Fig. 9. Half-bridge cell voltage controller.

circuit will have inherent balancing ability and does not even require additional balancing control. When needed, balancing control for lower cells can be used as shown in Fig. 9.

The reference cell voltage is calculated by averaging the capacitor voltages in half-bridge cells, i.e.,

$$v_{ref}^* = \frac{1}{M} \sum_{j=N+1}^{N+M} v_{Cj}^*$$

(13)

with  $v_{Cj}^{\ast}$  as the sampled capacitor voltage. As capacitor voltages contain considerable ac components, first-order lowpass filters are used. By comparing the reference voltage with the dc voltage of each cell, a proportional feedback control is used for regulation. A dead zone is created to allow a small tolerance of voltage imbalance. A saturation function is used to limit the adjustable range. As the current at the switching instant, and in average is positive while the cell capacitor is connected in series to the others, this capacitor voltage can be charged by increasing the cell duty cycle.

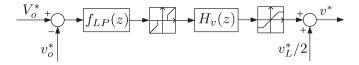

Fig. 10. General control for output voltage.

TABLE I

PARAMETERS OF THE APPLICATION EXAMPLE

| Symbol         | Quantity                   | Value                |

|----------------|----------------------------|----------------------|

| $\overline{P}$ | Power rating               | 1 MW                 |

| $V_L$          | Nominal low dc voltage     | 3 kV                 |

| $V_H$          | Nominal high dc voltage    | 30 kV                |

| $I_{pk}$       | Maximum device current     | 800 A                |

| $\dot{V}_{pk}$ | Maximum device voltage     | 8 kV                 |

| $\hat{f_s}$    | Switching frequency        | 1 kHz                |

| $T_e$          | Equivalent operating cycle | $250~\mu \mathrm{s}$ |

The general output voltage feedback control for all submodules is shown in Fig. 10. The voltage regulator is represented by  $H_v(z)$ , usually an antiwindup proportional-integral controller or a phase lead controller. The gain in this controller for submodules in the lower position is doubled compared with that in the upper position because of the duty-cycle differences (see Fig. 5). The pulse generated by the lower submodules is almost complementary to that of upper submodules.

### IV. STEP-UP CONVERTER APPLICATION EXAMPLE

The proposed converter can be used as a dc transformer with high step-up ratio. One interesting application of the proposed converter is to convert a low-voltage 400-V source into distribution voltage level (a few kilovolts). The converter can further be reconfigured with a transformer to provide isolation between input and output. This can boost the dc voltage with a very high step-up ratio and enables direct conversion from a wind turbine dc-link to a high-voltage direct current (HVDC) link for example. Due to the page limit, an isolated step-up converter is not considered further here.

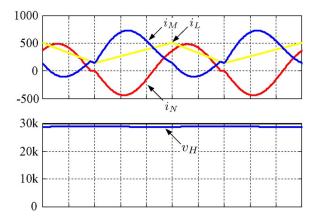

The application example discussed here is based on the proposed MMC dc–dc converter with two lower submodules (one redundant) and four upper submodules. It operates as a step-up converter from 3 to 30 kV. The application is a turbine converter delivering 1-MW power to a 30-kV medium-voltage dc collection bus. Series-connected ABB HiPak IGBT modules of type 5SNA 1200G450300 are used as the main switches. The parameters of this example are listed in Table I.

The simulation results of the step-up converter in the application example are shown in Fig. 11. The typical voltage drop across the IGBT is lower than 4 V, which is much smaller than the maximum switch voltage of 4.5 kV. In this example, the effect of the voltage drop can be considered negligible. The output voltage is a dc voltage with a ripple lower than 1%. As the converter is operating in resonant mode, the loss calculation is very complicated. According to IEC 61803, the losses measured in the HVDC converter are not likely to be a sufficient accurate indication of actual losses. Therefore, IEC 61803 standardizes a method of calculating the power losses. In additional to IEC 61803, the draft IEC 62751 breaks down power losses into individual components [21]. The power losses

Fig. 11. Simulated currents and output voltage of the converter. (X-axis: Time, 50  $\mu$ s/div; Y-axis: magnitude of current, 500 A/div; magnitude of voltage, 10 kV/div).

of the proposed converter have been calculated based on the simulation results.

The switching losses are comprised of the upper-stack IGBT switching losses  $P_{N1}^{\mathrm{sw}}$ , upper-stack diode reverse recovery losses  $P_{N2}^{\text{sw}}$ , lower-stack IGBT switching losses  $P_{M1}^{\text{sw}}$  and  $P_{M2}^{\text{sw}}$ . The clamping IGBTs in the upper stack are soft switched under a zero-current condition. The total energy loss when clamping IGBTs turn off is a function of the current  $i_N$  at that switching instant and so is written as  $E_{\text{off}}(i_N)$ . Therefore, the upper-stack clamping IGBTs' switching losses are calculated as  $P_{N1}^{\text{sw}} = 2N f_s E_{\text{off}}(i_N)$ . The clamped diodes in the upper stack are soft switched off so that the reverse recovery losses are negligible. The clamping IGBTs in the lower stack are soft switched on and off. However, their antiparallel diodes have reverse recovery losses as  $P_{M1}^{\mathrm{sw}}=4Mf_sE_{\mathrm{rr}}(i_M).$  The clamped IGBTs in the lower stack are hard switched on and off with the losses written as  $P_{M2}^{\text{sw}} = 4Mf_s E_{\text{off}}(i_M) + 4Mf_s E_{\text{on}}(i_M)$ . The total switching losses are

$$P_{\text{tot}}^{\text{sw}} = 2N f_s E_{\text{off}}(i_N) + 4M f_s E_{\text{rr}}(i_M) + 4M f_s E_{\text{off}}(i_M) + 4M f_s E_{\text{on}}(i_M).$$

(14)

The switching losses are obtained as  $P_{\mathrm{tot}}^{\mathrm{sw}}=35.2$  kW. The conduction losses comprise the upper-stack IGBT conduction losses  $P_{N1}^{\mathrm{con}}$ , upper-stack diode conduction losses  $P_{N2}^{\mathrm{con}}$ , lower-stack IGBT conduction losses  $P_{M1}^{\mathrm{con}}$ , and lower-stack diode conduction losses  $P_{M2}^{\mathrm{con}}$ . The saturation voltage  $V_{\mathrm{CE}}$  and forward voltage  $V_{\mathrm{F}}$  are functions of the current, which can be found from the datasheet. The conduction losses of the upper-stack IGBTs and diodes are given by  $P_{N1}^{\mathrm{con}}=2NI_NV_{\mathrm{CE}}(I_N)\lambda_{N1}$  and  $P_{N2}^{\mathrm{con}}=2NI_NV_{\mathrm{F}}(I_N)\lambda_{N2}$ , respectively. The factor  $\lambda$  represents the ratio of the conduction time to the switching period. The conduction losses of the lower stack are written as  $P_{M1}^{\mathrm{con}}=2MI_MV_{\mathrm{CE}}(I_M)\lambda_{M1}$  and  $P_{M2}^{\mathrm{con}}=2MI_MV_{\mathrm{F}}(I_M)\lambda_{M2}$ . The total conduction losses are

$$P_{\text{tot}}^{\text{con}} = 2NI_N V_{\text{CE}}(I_N) \lambda_{N1} + 2NI_N V_{\text{F}}(I_N) \lambda_{N2}$$

$$+ 2MI_M V_{\text{CE}}(I_M) \lambda_{M1} + 2MI_M V_{\text{F}}(I_M) \lambda_{M2}. \quad (15)$$

Summarizing the numerical result of the conduction loss calculation yields  $P_{

m tot}^{

m con}=7.7$  kW. The resistive losses mainly

TABLE II

EFFICIENCY VERSUS INPUT VOLTAGE

| Voltage [V] | 2000  | 4000  | 6000  | 8000  |

|-------------|-------|-------|-------|-------|

| Efficiency  | 90.6% | 93.2% | 94.0% | 94.3% |

come from the losses in the input inductor and the resonant inductor, represented by  $P_L^{\rm res}=I_L^2r_L$  and  $P_{L_s}^{\rm res}=I_N^2r_{L_s}$ , respectively. The total resistive losses are

$$P_{\text{tot}}^{\text{res}} = P_L^{\text{res}} + P_{L_s}^{\text{res}}.$$

(16)

The calculated resistive losses are  $P_{

m tot}^{

m res}=21.9$  kW. The total losses are calculated as

$$P_{\text{tot}}^{\text{loss}} = P_{\text{tot}}^{\text{sw}} + P_{\text{tot}}^{\text{con}} + P_{\text{tot}}^{\text{res}}.$$

(17)

The total power losses are calculated as  $P_{\rm tot}^{\rm loss}=64.8\,{\rm kW}$ . By comparing the ratio between power losses and output power, the efficiency in the application example is about 94%. As the switch voltages and currents are high, switching losses are more than half the total losses. The calculated efficiencies with 1-kHz switching frequency is shown in Table II. It can be seen that with voltage level increase, the efficiency is improved. Further improvement of efficiency could be achieved with fewer redundant submodules and reduced switching frequency. However, the cost would increase due to larger volume capacitors required.

The main disadvantage of a nonisolated dc-dc converter is the high current peak in the high-voltage side. A similar drawback exists in a conventional boost converter where the switch needs to withstand the high peak voltage and should be able to conduct the highest peak current. However, the proposed converter has a modular structure that is scalable in terms of voltage levels and avoids the difficulty of voltage sharing in a series connection of a large number of IGBTs. The equivalent switching frequency of the proposed converter is much higher than that of a standard boost converter while maintaining low switching frequency in each module. Moreover, it eliminates the use of bulky isolation transformers where entire high voltage applies on the insulation between windings. This converter may not suit all step-up applications, but where the voltage ratio is in the region of 10:1, the advantages of this converter may prove useful. In practice, a specific tradeoff should be made for the chosen application so that the converter can be properly configured.

# V. EXPERIMENTAL RESULTS

A downscaled experimental prototype with four upper cells and two lower cells was constructed based on the proposed circuit in Fig. 2(b) for verification. The submodules were implemented using capacitors with a nominal capacitance value of 50  $\mu$ F. As a result, the resonant frequency was expected to be approximately 4.1 kHz. The switching frequencies for upper cells and lower cells were fixed as 1 and 2 kHz, respectively, giving an effective operational frequency of 4 kHz, which is slightly less than the resonant frequency. The complete circuit parameters are listed in Table III.

TABLE III

PARAMETERS OF THE EXPERIMENTAL SYSTEM

| Symbol           | Quantity                    | Value                |

|------------------|-----------------------------|----------------------|

| $\overline{V_L}$ | Nominal low dc voltage      | 30 V                 |

| $V_H$            | Nominal high dc voltage     | 300 V                |

| $I_{pk}$         | Maximum switch current      | 30 A                 |

| $\dot{T_b}$      | Sampling period             | $100 \ \mu s$        |

| $T_e$            | Equivalent operating cycle  | $250~\mu \mathrm{s}$ |

| L                | Low voltage side inductor   | $821 \ \mu H$        |

| $L_s$            | Series inductor             | 120 $\mu H$          |

| C                | Cell capacitor              | $50 \mu F$           |

| $C_L$            | Low voltage side capacitor  | $470~\mu F$          |

| $C_H$            | High voltage side capacitor | $180 \mu F$          |

| $R_L$            | Low voltage side load       | $18 \Omega$          |

| $R_H$            | High voltage side load      | $1070~\Omega$        |

#### A. Open-Loop Tests

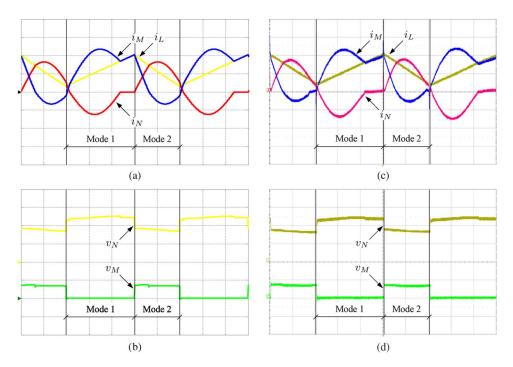

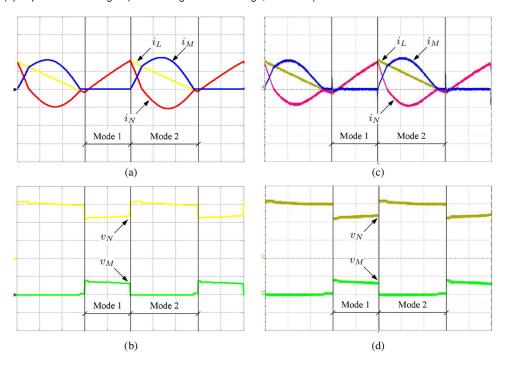

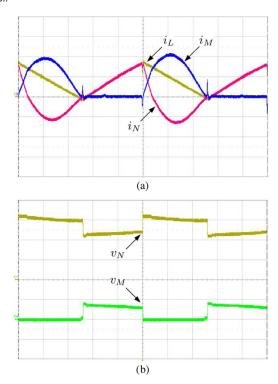

The open-loop tests used a fixed charging ratio of d = 0.6. For the step-up operation, the input voltage was 30 V, and the output voltage was expected to be 300 V. However, as the switches are not ideal, the high voltage will be lower than the expected value. For comparison purposes, the converter using the experimental parameters has been simulated. Fig. 12(a) and (b) shows the waveforms of simulated currents and voltages with voltage drop in each switch set to 1 V. The experimental current and voltage waveforms shown in Fig. 12(c) and (d) are quite similar to the corresponding simulation results. However, when the current  $i_N$  in Mode 1 cross zero from negative, the current resonance is dramatically damped compared with the simulation result in Fig. 11 (the application example) where this current is freely resonating. This is caused by the voltage drop across the switches (which appears relatively large in this downscaled prototype). When the current  $i_N$  is negative in Mode 1, the voltage drop across the diodes is positive compared with  $v_N$ . When the current  $i_N$  changes to positive, the voltage drop across the IGBTs becomes negative compared with  $v_N$ . Because in this mode the inductor L is charging and the capacitor  $C_H$  is discharging, the rise of current  $i_N$  is suppressed until the end of this mode. When Mode 2 begins, the inductor current  $i_L$  is discharged to the high-voltage side, and the current  $i_N$  keeps resonating until it reaches zero or the end of the equivalent operating cycle.

The simulated stack voltage waveforms in Fig. 12(b) are close to the experimentally measured stack voltage waveforms in Fig. 12(d). However, the upper-stack voltage  $v_N$  is lower than the expected amplitude. The sum of the lower-stack voltage and upper-stack voltage is far below 300 V. As a result, the conversion ratio is lower than 10:1. The output voltage should be adjusted by closed-loop control to achieve the required level.

For step-down operation, the input high voltage was set to 300 V. The output low voltage is expected to be 30 V. However, as there are voltage drops in the real switches, the output voltage may be lower than expected. Fig. 13(a) and (b) shows the simulated step-down current and voltage waveforms with 1-V voltage drop in each switch. In contrast, the experimental step-down current and voltage waveforms in Fig. 13(c) and (d) are quite similar to the relevant simulation results. The inductor L is charging in Mode 1 and discharging in Mode 2. The lower-stack current is zero during this mode. The currents  $i_L$  and  $i_N$  should linearly increase in Mode 1 and  $i_L$  equals  $i_N$ . In Mode 2,

Fig. 12. Simulation and experimental waveforms of the proposed converter for step-up conversion (X-axis: time, 50 μs/div). (a) Simulated currents (Y-axis: magnitude of current, 2 A/div). (b) Simulated voltages (Y-axis: magnitude of voltage, 100 V/div). (c) Experimental currents (Y-axis: magnitude of current, 2 A/div). (d) Experimental voltages (Y-axis: magnitude of voltage, 100 V/div).

Fig. 13. Simulation and experimental waveforms of the proposed converter for step-down conversion (X-axis: time, 50  $\mu$ s/div). (a) Simulated currents (Y-axis: magnitude of current, 2 A/div). (b) Simulated voltages (Y-axis: magnitude of voltage, 100 V/div). (c) Experimental currents (Y-axis: magnitude of current, 2 A/div). (d) Experimental voltages (Y-axis: magnitude of voltage, 100 V/div).

the current  $i_L$  starts to linearly decrease. All the cell capacitors in the upper stack are in series with the inductor  $L_s$ , forming a resonant tank for  $i_N$  to discharge. The stack voltage waveforms are in accordance with the waveforms in Fig. 6. This verifies the operation analysis of the proposed converter. The output high voltage is around 25 V with  $v_H=300$  V under open-loop control. The output voltage is lower than the expected value due to the voltage drop across the IGBTs.

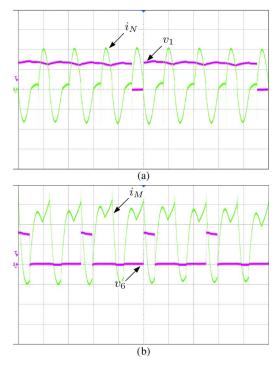

The current and voltage waveforms of submodules in stepup operation are shown in Fig. 14. As Cell 1 can represent all the upper cells and Cell 6 can represent the lower cells, the waveforms of Cell 1 and Cell 6 are shown. It can be seen in Fig. 14(a) that the resonant current frequency is 4 kHz and the switching frequency of upper cells is 1 kHz. As explained in the previous sections, the interleaved PWM can quadruple the equivalent operating frequency. The switch-on and switch-off

Fig. 14. Experimental step-up submodule current and voltage of the clamped switch of (a) Cell 1 and (b) Cell 6 (X-axis: time, 200  $\mu$ s/div; Y-axis: magnitude of current, 2 A/div; magnitude of voltage, 50 V/div).

currents in the clamped switch of the upper cells are low. In the lower stack [see Fig. 14(b)], the clamped switch of Cell 6 has a switching frequency of 2 kHz. However, the current flowing through has an equivalent frequency of 4 kHz. This verifies the operation principle of the interleaved PWM control.

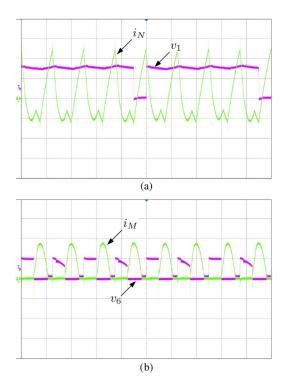

The step-down operation results are also provided. The current and voltage waveforms of submodules in step-down operation are shown in Fig. 15. The waveforms of Cell 1 and Cell 6 are shown. It can be seen in Fig. 15(a) that the resonant current frequency is 4 kHz and the switching frequency of upper cells is 1 kHz. The equivalent operating frequency is increased by the interleaved PWM. The resonant frequency is four times as high as the switching frequency. In Cell 6 of the lower stack [see Fig. 15(b)], the cell current has an equivalent frequency of 4 kHz. As the current is zero when the clamping IGBT in Cell 6 is switched off, the voltage of the clamped diode in Cell 6 can have a voltage lower than the cell capacitor voltage. However, the actual switching frequency used in Cell 6 is still 2 kHz.

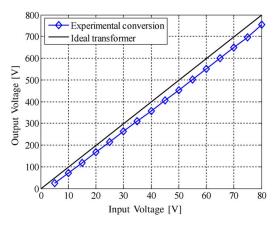

## B. Linearity Tests

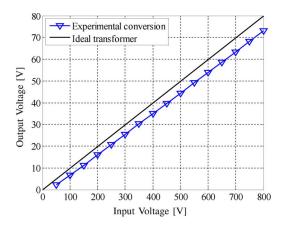

The linearity of the output voltage versus the input voltage of the step-up operation is tested. Fig. 16 shows how the output (high-side) voltage varies as the input (low-side) voltage is changed for a fixed charging ratio of d=0.6 (that is, open-loop operation) and also the characteristic of an ideal dc transformer. The circuit shows a linear relation between output and input voltages but with an offset compared with the ideal case. This offset is accounted for by the conduction voltage drops of the IGBTs and diodes of the submodules. The low submodule voltage in this downscaled prototype results in a noticeable relative error in Fig. 16 when the input voltage is particularly low.

Fig. 15. Experimental step-down submodule current and voltage of the clamped switch of (a) Cell 1 and (b) Cell 6 (X-axis: time, 200  $\mu$ s/div; Y-axis: magnitude of current, 2 A/div; magnitude of voltage, 50 V/div).

Fig. 16. Experimentally measured step-up high voltages versus different input low voltages.

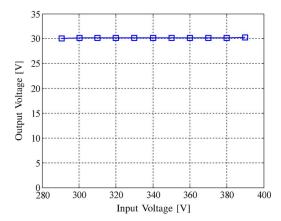

Furthermore, the linearity of the output voltage versus the input voltage of the step-down operation is shown in Fig. 17. The circuit shows a linear relation between output and input voltages but with an offset compared with the ideal dc transformer. This offset is due to voltage drops across the semiconductors. The relative error in Fig. 17 reduces when the input voltage is increased. When the cell voltage approaches the rated voltage, the step-down ratio will be close to the ideal value.

# C. Closed-Loop Tests

Closed-loop control was applied to test the regulation properties of the converter. The output voltages were fed back to change the charging ratio.

Fig. 17. Experimentally measured step-down low voltages versus different input high voltages.

Fig. 18. Experimental waveforms of the closed-loop control step-up conversion (X-axis: Time, 50  $\mu$ s/div). (a) Experimental currents (Y-axis: magnitude of current, 2 A/div). (b) Experimental voltages (Y-axis: magnitude of voltage, 100 V/div).

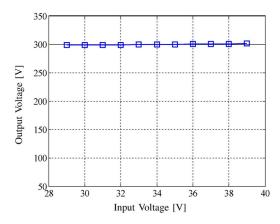

Fig. 18 shows the experimental waveforms of the closed-loop controlled step-up conversion. The input low voltage was fixed as  $v_L=30\,\mathrm{V}$ . Compared with the waveforms under open-loop control with d=0.6 (see Fig. 12), it can be seen that the charging ratio d in the closed-loop curve has been raised by the controller. As a result, the step-up conversion ratio of 10:1 is achieved such that the high voltage  $v_H$  is almost 300 V. Fig. 19 shows the experimentally measured step-up voltages under closed-loop control. It can be observed that the closed-loop controller is effective that the high voltage is always controlled around the rated value 300 V.

Fig. 20 shows the experimental current and voltage waveforms of the closed-loop controlled step-down conversion. The input high voltage was fixed as  $v_H = 300$  V. Compared with

Fig. 19. Experimentally measured step-up voltages with closed-loop control.

Fig. 20. Experimental waveforms of the closed-loop control step-down conversion (X-axis: Time, 50  $\mu$ s/div). (a) Experimental currents (Y-axis: magnitude of current, 2 A/div). (b) Experimental voltages (Y-axis: magnitude of voltage, 100 V/div).

the waveforms under open-loop control with d=0.6 (see Fig. 13), it can be seen that the charging ratio d in the closed-loop controlled converter has been reduced. Fig. 21 shows the experimentally measured output voltages under closed-loop control. It can be seen that the closed-loop controller is effective that the low voltage is always regulated around the rated value 30 V. The capacitor voltages were also measured. Under nominal input voltage conditions, the voltages in upper submodules are balanced with each other, and the voltages in lower submodules are balanced as well.

#### VI. CONCLUSION

The new transformerless MMC dc-dc converter has been presented and analyzed. Two stacks of submodules in series

Fig. 21. Experimentally measured step-down voltages with closed-loop control.

arrangement support the high voltage. The dc capacitors of the submodules are used also for resonant operation. The proposed converter has a bidirectional conversion ability. The step-up operation and the step-down operation are demonstrated. This converter is capable of operating under open-loop control as a dc transformer with good linearity. Alternatively, closed-loop control can be applied for trimming of the output voltage. The operating principle was verified through a bench-scale experimental prototype. The proposed converter may exhibit relatively high losses because of the high ac current that resonates in the submodules, but reasonably high efficiency was shown to be possible in high-voltage applications. Further efficiency improvement can be achieved with lower switching frequency, but cell capacitors with a higher volume will be required. The converter can achieve a large step-up conversion ratio without the use of transformers. The proposed converter has the features of modularity, scalability, and simplicity, and these may make it attractive in some special applications.

#### REFERENCES

- [1] S. Kouro *et al.*, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [2] J. I. Leon et al., "Multidimensional modulation technique for cascaded multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 58, no. 2, pp. 412– 420, Feb. 2011.

- [3] M. A. Perez, J. Rodriguez, E. J. Fuentes, and F. Kammerer, "Predictive control of ac–ac modular multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 7, pp. 2832–2839, Jul. 2012.

- [4] E. Solas et al., "Modular multilevel converter with different submodule concepts—Part II: Experimental validation and comparison for HVDC application," *IEEE Trans. Ind. Electron.*, vol. 60, no. 10, pp. 4536–4545, Oct. 2013

- [5] J. Ferreira, "The multilevel modular dc converter," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4460–4465, Oct. 2013.

- [6] M. Perez, S. Bernet, J. Rodriguez, S. Kouro, and R. Lizana, "Circuit topologies, modelling, control schemes and applications of modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 4–17, Jan. 2015.

- [7] T. A. Meynard and H. Foch, "Multi-level conversion: High voltage choppers and voltage-source inverters," in *Proc. IEEE Power Electron. Spec. Conf.*, 1992, pp. 397–403.

- [8] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 611–618, Mar./Apr. 2001.

- [9] S. Busquets-Monge, S. Alepuz, and J. Bordonau, "A bidirectional multilevel boost-buck dc-dc converter," *IEEE Trans. Power Electron.*, vol. 26, no. 8, pp. 2172–2183, Aug. 2011.

- [10] T. Todorcevic, P. Bauer, J. A. Ferreira, and R. van Kessel, "Bidirectional modular multilevel dc-dc converter control and efficiency improvements through separate module control method," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2013, pp. 2038–2043.

- [11] K. D. T. Ngo and R. Webster, "Steady-state analysis and design of a switched-capacitor dc-dc converter," *IEEE Trans. Aerop. Electron. Syst.*, vol. 30, no. 1, pp. 92–101, Jan. 1994.

- [12] F. Khan and L. Tolbert, "A multilevel modular capacitor-clamped DC–DC converter," *IEEE Trans. Ind. Appl.*, vol. 43, no. 6, pp. 1628–1638, Nov./Dec. 2007.

- [13] D. Cao and F. Z. Peng, "Zero-current-switching multilevel modular switched-capacitor DC–DC converter," *IEEE Trans. Ind. Appl.*, vol. 46, no. 6, pp. 2536–2544, Nov./Dec. 2010.

- [14] G. Ortiz, H. Uemura, D. Bortis, J. W. Kolar, and O. Apeldoorn, "Modeling of soft-switching losses of IGBTs in high-power high-efficiency dualactive-bridge dc/dc converters," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 587–597, Feb. 2013.

- [15] C.-M. Young, M.-H. Chen, T.-A. Chang, C.-C. Ko, and K.-K. Jen, "Cascade Cockcroft–Walton voltage multiplier applied to transformerless high step-up dc–dc converter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 2, pp. 523–537, Feb. 2013.

- [16] M. Kasper, D. Bortis, and J. W. Kolar, "Novel high voltage conversion ratio rainstick dc/dc converters," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2013, pp. 789–796.

- [17] X. Zhang, T. C. Green, and A. Junyent-Ferre, "A new resonant modular multilevel step-down dc-dc converter with inherent-balancing," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 78–88, Jan. 2015.

- [18] T. Luth, M. M. C. Merlin, T. C. Green, F. Hassan, and C. D. Barker, "High-frequency operation of a dc/ac/dc system for HVDC applications," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4107–4115, Aug. 2014.

- [19] S. Allebrod, R. Hamerski, and R. Marquardt, "New transformerless, scalable modular multilevel converters for HVDC-transmission," in *Proc. IEEE PESC*, 2008, pp. 174–179.

- [20] A. Antonopoulos, L. Angquist, L. Harnefors, K. Ilves, and H.-P. Nee, "Global asymptotic stability of modular multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 61, no. 2, pp. 603–612, Feb. 2014.

- [21] P. S. Jones and C. C. Davidson, "Calculation of power losses for MMC-based VSC HVDC stations," in *Proc. EPE*, 2013, pp. 1–10.

Xiaotian Zhang (S'11–M'12) was born in Xi'an, China, in 1983. He received the B.S. (with honors) and M.S. degrees in electrical engineering from Jiaotong University, Xi'an, in 2006 and 2009, respectively, and the Ph.D. degree (with honors) in electrical engineering and electronics from the University of Liverpool, Liverpool, U.K., in 2012.

Since 2013, he has been with the Department of Electrical Engineering, Imperial College London, London, U.K. His research interests

include control modeling and circuit design of multilevel converters for high-voltage applications.

**Timothy C. Green** (M'89–SM'02) received the B.Sc. degree (first-class honors) in electrical engineering from Imperial College London, London, U.K., in 1986 and the Ph.D. degree in electrical engineering from Heriot-Watt University, Edinburgh, U.K., in 1990.

He was a Lecturer with Heriot-Watt University until 1994 and is currently a Professor of electrical power engineering with Imperial College London, the Deputy Head of the Electrical and Electronic Engineering Department, and the Di-

rector of the Energy Futures Laboratory. His research interest is in formulating the future from the electricity network to support low-carbon futures. A particular theme is how the flexibility of power electronics and control can be used to accommodate new-generation patterns and new forms of load, such as EV charging, as part of the emerging smart grid. He has particular interest in offshore dc networks and the management of low-voltage networks. He leads the HubNet consortium of eight U.K. universities coordinating research in low-carbon energy networks and is the Network Champion for the Research Councils U.K.

Dr. Green is a Chartered Engineer in the U.K.